Through MIPSfpga, Imagination is offering access to a fully-validated, current generation MIPS CPU RTL in a complete teaching package.

CPU architecture is generally taught as part of electronic engineering, computer science and computer engineering courses, and is based on MIPS or one of the other two major CPU architectures. The MIPS architecture started off as an academic exercise by John Hennessy at Stanford University, and is the subject of a standard educational book by Hennessy and David Patterson,

Until now, what’s been missing from all of these courses is access to real, un-obfuscated RTL code that will enable professors and students to study and explore a real CPU.

The CPU is being offered as part of a complete free-to-download package for universities, together with a Getting Started Guide, teaching guide for professors, and examples designed to enable students to see how the CPU works and explore its capabilities. With the materials, students can develop a CPU and take it through debug, running on an FPGA platform.

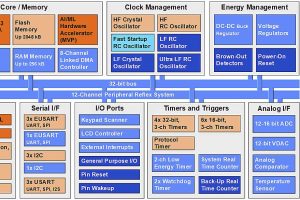

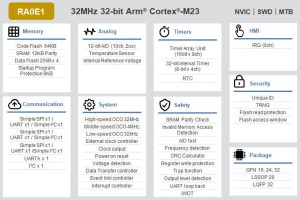

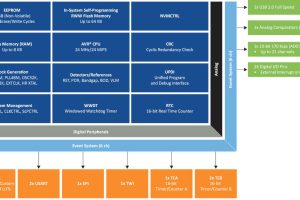

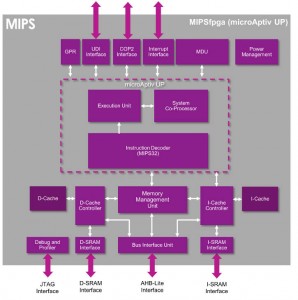

In particular, it is making available RTL for the microAptive core – as used by Microchip in PIC32MZ microcontrollers.

“Usually universities are provided with cores that have been obfuscated – they look like a black box. I have been talking to professors all over the world, and they want a core where they can get under the hood. THe students need to take the lid off, see how it works and modify it,” Imagination University programme manager Robert Owen told Electronics Weekly.

The core is not exactly the core used by Microchip, but neither is it dumbed-down – it has a memory mangement unit (MMU), cache controller and JTAG boundary scan, for example.

It consists of a set of microAptive options selected by Professor David Harris, co-author of the book ‘Digital Design and Computer Architecture’. Professor Sarah Harris, the other author, has developed the MIPSfpga teaching materials.

One of the drivers for option selection, like the inclusion of a cache controller, was to make this a Linux-capable MicroAptive core.

As its name suggests, it is designed to be run in an FPGA, and guides are available to use it on the Digilent Nexys4 (Xilinx Artix-7) and the Terasic DE2 (Altera Cyclone) platforms. Some additional blocks, and driver software, are under development to get Linux up and running on the FPGAs – expected within three months.

To use the core, universities will have to register with Imagination – Harvey Mudd College California, Imperial College London, University College London (UCL), and the University of Nevada, Las Vegas, have already done so.

Lecturers will have to sign a licence. “It is a very simple licence in plain English,” said Owen.

Taking the wraps off architectural RTL is not without risk as all or part of it could end up illegally copied.

Imagination has thought long and hard about the implication, and thinks releasing the IP is worth it, said Owen, pointing out that the MIPS organisation is used to dealing with companies who use its instruction set without permission, and their customers. “I don’t think we are going to end up chasing lecturers if it gets put in silicon illegally,” he added.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News